Flash-Produktion der Zukunft strebt nach Höherem, Teil 2 Halbleiterhersteller entdecken die vierte Dimension

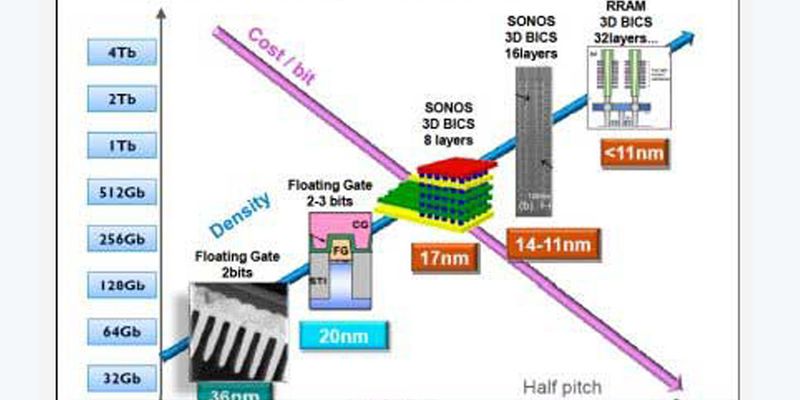

Die Flächendichte von Speicherzellen lässt sich nur noch mit immer größerem Aufwand verkleinern. Nur mit einer Erweiterung in die dritte Dimension kann die Speicherkapazität mit gleichbleibendem Tempo ausgeweitet werden. Die Definition von Fortschritt ist deshalb häufig eine Frage der Definitionshoheit.

Anbieter zum Thema

Während sich die Physik an der Frage abarbeitet wo der Ereignishorizont des Urknalls liegt, arbeiten sich Halbleiterhersteller langsam aber sicher an die technische Kante voran, ob man mit einer Atomlage noch ausreichend Material besitzt für die Speicherung einer Informationseinheit besitzt.

Vorderhand geht es allerdings um die Frage, wie weit kann man mit der Flash-Technik noch Geld verdienen, oder sind andere Technologien geeigneter das Verhältnis von Kosten pro Bit zu verbessern. Etwa 2014 wird sich entscheiden, ob die Nachfolgetechniken eine Chance bekommen.

2D, 3D, 4D & TSV

Die bisher übliche Planartechnik wird 2D genannt. Sind die Strukturen innerhalb einer Zellenebene schon dreidimensional, dann wird das oft schon mit 3D gekennzeichnet. Werden mehrere Chips ohne Gehäuse ("dies") bei der Herstellung übereinandergelegt und direkt miteinander verbunden, dann wird dies je nach Hersteller auch als 3D oder gar als 4D angepriesen.

Die Experten wollen jedoch die Bezeichnung 3D nur für Chips verwenden, die auf einem Substrat so viele Lagen (Zellenebenen) aufgebaut haben, dass die Funktionsblöcke (ohne Zwischensubstrate) direkt übereinander liegen. Dazu wird beispielsweise die "Through-Silicon-Via"-Technik (TSV) benötigt. Die Verbindungsleitungen werden also senkrecht von Lage zu Lage durchgeätzt und mit leitendem Material ausgefüllt.

Die BiCS-Technik ("Bit Cost Scaling") von Toshiba ist so eine 3D-Technik, die auf den Weg zur Produktionsreife gebracht wird. In ferner Zukunft sollen damit Kapazitäten von zehn TBit/Chip erreicht werden. Bei Samsung gibt es die "Terabit Cell Array Transistor"-Technik (TCAT) für 3D-Flash.

Gate first/last

Bei der Produktion gibt es Varianten, die als "gate first" oder "gate last" bezeichnet werden. Beide Herstell-Techniken haben Vor- und Nachteile:

- gate first wird auch "metal inserted poly-silicon" (MIPS) genannt)

- gate last wird auch "replacement metal gate" (RMG) genannt)

Dabei beziehen sich das "first" (zuerst) und "last" (zuletzt) darauf, ob die Gate-Elektrode vor (first) oder nach (last) der Aktivierung der Source- und Drain-Gebiete hergestellt wird. Weitere Bezeichnungen bei gate last sind: "replacement gate" (RG) oder "damascene gate". Außerdem gibt es noch das "fully silicided gate" (FUSI).

Der Vorteil beim "gate first"-Prozess ist, dass die Prozessreihenfolge der eines Polysilicium-Gates entspricht, also weniger Anpassungen an den Herstellungsprozess notwendig sind.

Beim "gate last"-Prozess ist die geringere thermische Belastung des "high-k"-Materials und der Metallschichten von Vorteil, weil die Hochtemperaturschritte bereits vorher durchgeführt werden. Nachteilig ist der höhere Aufwand bei der Fertigung, weil hohe Genauigkeiten und unterschiedlichen Materialien den Prozessablauf erschweren.

Weiterentwicklung

Während die Verkleinerung der Funktionselemente rasch voranschreitet, verschlechtern sich alle anderen Parameter (Leistung, Zahl der Schreib-/Lesezyklen, Energieeffizienz, Datenerhaltung) zum Teil exponentiell. So verlängert sich die Schreib-Latenzeit etwa um den Faktor vier für jedes zusätzliche Bit je Zelle.

Die Anzahl der Programmierzyklen nimmt um den Faktor zehn oder mehr ab. Auch die Zellendichte nimmt nicht linear mit der Bit-je-Zellen-Dichte zu.

Die Strukturgrößen 1Y und 1Z (siehe Textbox: "feature size") können mit der bisherigen Planartechnik (2D) nur mit großen Anstrengungen gemeistert werden. Unterhalb von 10 Nanometer (nm) werden wohl 3D-Varianten eingesetzt. Größere Produktionsmengen werden von der Industrie für den Zeitraum 2014 bis 2016 angekündigt.

(ID:37987130)

:quality(80)/p7i.vogel.de/wcms/b5/ad/b5ade2e50671d986cabb091cc33de39f/0127234511v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2d/69/2d69b27f3f8f5f290f7ae2b3d9123b1b/0127206601v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/d2/94d28e3faac411c22b54d80ea354d2e3/0124559320v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/8a/b48ab01d140056118571c14dfeafe4b1/0130911722v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/47/9b47ec5489e17a326e023da87a077d66/0130088124v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/cc/04ccc504aee183fd610969ddf31ebbc1/0130625872v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/dd/df/dddf319803b27a98ff9974c4258ecd2e/0130916737v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/28/f228ec57e5d8978ff8bf6da2448566bd/0130957183v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/39/bb39974cb4de565d138bd500f418f834/0130876455v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c8/b9/c8b9e2a116fb3366a8a00427ecc10557/0130541481v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/d9/ffd9bfea2f2b5161c0fad701c74850cb/0131123001v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/58/195816925f598f07ceffbcaed6fa8486/0131065514v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/d6/cdd6fc25c704ffe9ab6afc24ec68725e/0130507132v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/b9/08b906f0ef0c5ad843b0ce1a09335985/0130533152v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/e2/37e239c7ec0154c8c93688ca2554af48/0130578270v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/c8/48c8f436d680ea980781cbd728c109c1/0129826847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c1/81/c1811ad769ce2c6fe9e5bfb2c8775591/0130016264v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/55/b75581013900f582f2200a2d53e23359/0130382558v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/bd/0a/bd0a232a32dc365e8e19c2ad5a2aeb43/0130082482v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/07/c70745f1f1cb46fcc5d05b756a0697f5/0131065289v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/f3/cdf30cf240d9e2f92e9529458eb9914b/0130632554v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/c2/d2c28ed803c9d554134d0f667c0b6979/0130964136v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/3b/96/3b963ec05404af359f9e7c4f23e389e8/0130942788v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/38/07382204cc163f3172de0a99dc5d6abf/0130936373v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f8/db/f8dbe2337659dd44bdf89efec6cfcf1a/0129529497v1.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1552300/1552323/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1644500/1644561/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1641800/1641842/original.jpg)

:fill(fff,0)/p7i.vogel.de/companies/68/2d/682dd583dcc4c/fsas-afc-horizontal-2-positive-rgb-nov24.png)

:quality(80)/p7i.vogel.de/wcms/44/47/4447cd32e22eb986a40bdfbd4d391cfb/0124351672v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4e/c5/4ec5852490fafcb5691f39da92157e5e/0127608232v1.jpeg)