3D Vertical NAND-Flash- und SSD-Lösungen, Teil 1 Dimensionsverschiebungen bei Samsungs Flash-Produktion

Im August 2013 stellte Samsung Electronics den industrieweit ersten dreidimensionalen Vertical NAND (V-NAND) Flash-Speicher vor, der die Skalierungsgrenzen der derzeit verfügbaren NAND-Flash-Technologie überwindet. Klingt aufregend, machte aber in der Halbleiterfertigung einige Optimierungsschritte notwendig.

Anbieter zum Thema

Der neue 3D V-NAND weist verbesserte Leistungsfähigkeit und Flächenverhältnisse auf. Der Speicher wurde für eine Vielzahl von Anwendungen in in der Unterhaltungselektronik und im Enterprise-Bereich, darunter Embedded NAND Storage und SSDs (Solid State Drives), entwickelt.

Der neue V-NAND von Samsung verfügt über eine Speicherkapazität von 128 Gigabit (GBit) auf einem Chip. Es nutzt die proprietären vertikalen Zellenstrukturen des Unternehmens, die auf den beiden Technologien 3D Charge Trap Flash (CTF) und Vertical Interconnect (VI) zur Verbindung des 3D-Zellen-Arrays basiert.

Rechenzentrums-tauglich

Durch die Anwendung der beiden Technologien kann der 3D V-NAND von Samsung mehr als die doppelte Skalierung von 20nm-Class* Planar NAND Flash bereitstellen.

Im selben Monat folgte die erste 3D Vertical NAND Speicher Massenproduktion. Gleichzeitig wird die 3D V-NAND basierte Solid State Drive (SSD) in der 960 GB und 480 GB Version mit über 20 Prozent höheren sequenziellen und Random Schreibgeschwindigkeiten vorgestellt. Genutzt werden 64 Dies an MLC 3D V-NAND Flash mit jeweils 128 GBit und einem SATA-Schnittstellen-Controller mit sechs Gigabit/s.

Die 3D V-NAND Technologie und die 3D V-NAND basierte SSD von Samsung überwinden das Moore’sche Gesetze und ermöglichen den Kunden, ihre Systeme mit höherer QoS (Quality of Service) zu optimieren. Beides ist für Rechenzentrums- und Cloud-Server-Anwendungen entscheidend.

3D-V-NAND-Lösungen überwinden das Moore’sche Gesetz

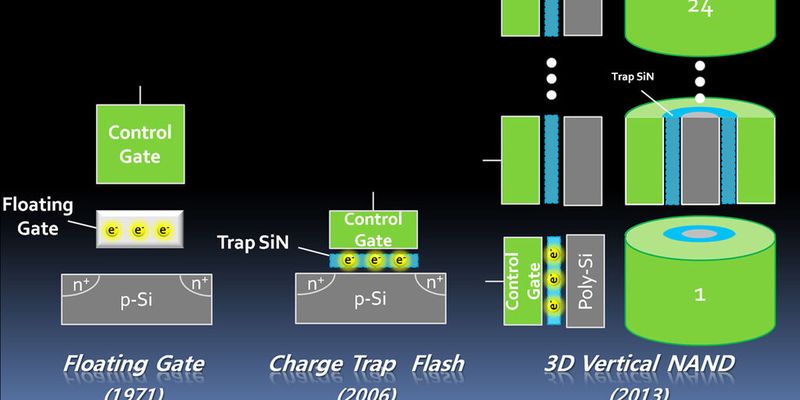

In den vergangenen 40 Jahren beruhte herkömmliche Flash-Speicher auf planaren Strukturen mit Floating-Gates. Da sich die Fertigungstechnologie hin zur 10 nm-Class* und niedriger entwickelt hat, sind aufgrund der Interferenzen zwischen den Zellen, die die Zuverlässigkeit von NAND-Flash-Produkten beeinträchtigen können, Bedenken hinsichtlich der Skalierungsgrenzen aufgekommen.

Das führte zu längeren Entwicklungszeiten und höheren Kosten. Samsung überwindet diese Grenzen in der Halbleiterbranche mit 3D-V-NAND-Lösungen, die auf einer zylinderförmigen 3D Charge Trap Flash Cell-Architektur und vertikaler Interconnect-Prozesstechnologie basieren.

Zylinderförmige 3D-Charge-Trap-Flash- Zellenstrukturen

Der neue V-NAND von Samsung überwindet die technischen Herausforderungen, mit innovativen Schaltkreisen, Strukturen und Fertigungsprozessen. Das vertikale Stacking planarer Zellenschichten wurde erfolgreich für eine neue 3D-Struktur entwickelt.

(ID:42722421)

:quality(80)/p7i.vogel.de/wcms/b5/ad/b5ade2e50671d986cabb091cc33de39f/0127234511v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2d/69/2d69b27f3f8f5f290f7ae2b3d9123b1b/0127206601v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/d2/94d28e3faac411c22b54d80ea354d2e3/0124559320v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b4/8a/b48ab01d140056118571c14dfeafe4b1/0130911722v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/9b/47/9b47ec5489e17a326e023da87a077d66/0130088124v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/04/cc/04ccc504aee183fd610969ddf31ebbc1/0130625872v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/dd/df/dddf319803b27a98ff9974c4258ecd2e/0130916737v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f2/28/f228ec57e5d8978ff8bf6da2448566bd/0130957183v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/bb/39/bb39974cb4de565d138bd500f418f834/0130876455v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c8/b9/c8b9e2a116fb3366a8a00427ecc10557/0130541481v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ff/d9/ffd9bfea2f2b5161c0fad701c74850cb/0131123001v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/19/58/195816925f598f07ceffbcaed6fa8486/0131065514v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/d6/cdd6fc25c704ffe9ab6afc24ec68725e/0130507132v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/b9/08b906f0ef0c5ad843b0ce1a09335985/0130533152v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/37/e2/37e239c7ec0154c8c93688ca2554af48/0130578270v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/c8/48c8f436d680ea980781cbd728c109c1/0129826847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c1/81/c1811ad769ce2c6fe9e5bfb2c8775591/0130016264v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/55/b75581013900f582f2200a2d53e23359/0130382558v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/bd/0a/bd0a232a32dc365e8e19c2ad5a2aeb43/0130082482v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c7/07/c70745f1f1cb46fcc5d05b756a0697f5/0131065289v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/cd/f3/cdf30cf240d9e2f92e9529458eb9914b/0130632554v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/d2/c2/d2c28ed803c9d554134d0f667c0b6979/0130964136v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/3b/96/3b963ec05404af359f9e7c4f23e389e8/0130942788v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/07/38/07382204cc163f3172de0a99dc5d6abf/0130936373v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f8/db/f8dbe2337659dd44bdf89efec6cfcf1a/0129529497v1.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1552300/1552323/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1644500/1644561/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1641800/1641842/original.jpg)

:fill(fff,0)/p7i.vogel.de/companies/69/98/699837ff85e16/datacore-logo-700x700px.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/63/db/63dbd1915b7af/2023-fastlta-logo-square-positive.jpeg)

:quality(80)/p7i.vogel.de/wcms/59/f6/59f6d76c97ab4fddf39621771f044ba2/0125715379v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ba/eb/baebc46a7fee5c8aa2d02813d9bcc127/0126734553v1.jpeg)