Anbieter zum Thema

Serielle interne Hoch- und Höchtgeschwindigkeits-Schnittstellen

PCI (Peripheral Component Interconnect)

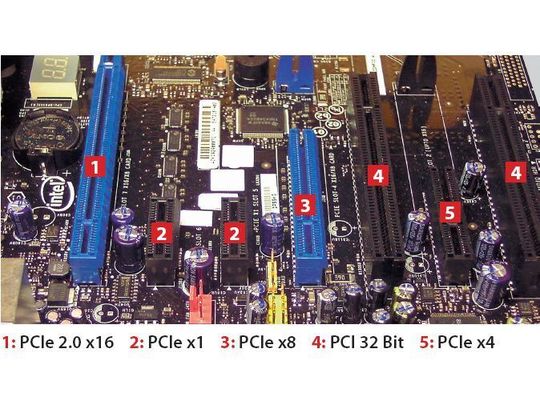

Schnittstellen auf dem Motherboard: 2x PCI 2.0

- Paraller synchroner Bus für Steckkarten mit 32 Bit Datenbreite

Hinweis: Die Brutto-Bandbreite hängt von der Taktfrequenz und Datenbreite ab. Bei 33 MHz Takt lassen sich 133 MByte/s, bei 66 MHz können bis zu 266 MByte/s transferiert werden. Das reicht allerdings weder für moderne Grafikkarten und nur ganz knapp für 1 GBit/s Netzwerkkarten aus.

Der PCI-Bus ist inzwischen 20 Jahre alt und führt auf Intels DP55KG nur noch ein Schattendasein. Eine zukunftsorientierte Backup-Strategie sollte nicht auf den PCI-Bus setzen.

PCIe (Peripheral Component Interconnect Express)

Schnittstellen auf dem Motherboard: 2x PCIe 1.0 x1; 1x PCIe 2.0 x8/x16 (Grafik 1), 1x PCIe 1.0 x8 (Grafik 2)

- Serielle Punkt zu Punkt Verbindung (Lane) für Steckkarten, deren Leistungsfähigkeit sich durch die Koppelung von 4, 8, 16 Lanes erhöhen lässt.

- Bandbreite PCIe 1.0 x1: 250 MByte/s

- Bandbreite PCIe 1.0 x4: 250 – 1000 MByte/s

- Bandbreite PCIe 1.0 x8: 250 - 2000 MByte/s

- Bandbreite PCIe 2.0 x16: 500 - 8000 MByte/s

- Flaschenhals bei: 720 GByte/h – 28,8 TByte/h

Hinweis: Die Leistungsfähigkeit von PCIe wird seit Version PCIe 1.0 x1 zusätzlich durch die Erhöhung der Takfrequenz von 250 MHz über Version 2.0 mit 500 MHz und Version 3.0 mit 1000 MHz gesteigert.

Die Abwärtskompatibilität ist nur für PCIe x1 sichergestellt, Bei x4- und x8-Karten in x8- oder x16-Slots kann Abwärtskompatibilität umgesetzt sein, es existieren aber keine zwingend einzuhaltenden Standards.

PCIe 3.0 (ab 2011)

Serielle Punkt zu Punkt Verbindung (Lane) für Steckkarten, deren Leistungsfähigkeit sich durch die Koppelung von bis zu 32 Lanes erhöhen lässt.

PCIe 3.0 ist für den Datentranfer mit Solid State Disks (SSD) optimiert, so dass SSD-Zugriffe ohne Verzögerung von der CPU gelesen werden können.

(ID:2044005)

:quality(80)/p7i.vogel.de/wcms/b5/ad/b5ade2e50671d986cabb091cc33de39f/0127234511v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2d/69/2d69b27f3f8f5f290f7ae2b3d9123b1b/0127206601v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/94/d2/94d28e3faac411c22b54d80ea354d2e3/0124559320v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/08/b9/08b906f0ef0c5ad843b0ce1a09335985/0130533152v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/92/fa/92fa56077ccd3ff878b6a85ce4de1d32/0130727055v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/68/ff/68ff1f86c3747efa69a932a2b29e2e6f/0130912670v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/2c/31/2c310e263bd5f3746b66eb0b0eb711dd/0130707872v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/86/06/86068cee815dbb389250a7655f0d55d3/0130597756v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/e2/c6/e2c6f15bf37815bceeb83b5b69698ea1/0130563514v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/c8/48c8f436d680ea980781cbd728c109c1/0129826847v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ac/fe/acfef93609c37a7ea61b1e3244dea967/0130620671v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/48/81/488147108a520bc67dadbdf1c59178c7/0129710650v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/c1/81/c1811ad769ce2c6fe9e5bfb2c8775591/0130016264v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/b7/55/b75581013900f582f2200a2d53e23359/0130382558v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/bd/0a/bd0a232a32dc365e8e19c2ad5a2aeb43/0130082482v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/4a/37/4a3731ad57c47e87cfedcd5342b9a4da/0129713569v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/02/2f/022f4cf56715e098d0cfb1c97812038e/0130515238v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/24/3e/243e149198de7d0ac862c3edc694bfe4/0130490930v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/f8/db/f8dbe2337659dd44bdf89efec6cfcf1a/0129529497v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/fe/18/fe181da82b3e76596f4d461a5920a33a/0129473576v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/ca/3f/ca3f194f4553759bea537346bc9e3988/0129465088v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/dc/77/dc775d60ab66327e5946ba9dda5ca838/0129420829v1.jpeg)

:quality(80)/images.vogel.de/vogelonline/bdb/1552300/1552323/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1644500/1644561/original.jpg)

:quality(80)/images.vogel.de/vogelonline/bdb/1641800/1641842/original.jpg)

:fill(fff,0)/p7i.vogel.de/companies/63/db/63dbd1915b7af/2023-fastlta-logo-square-positive.jpeg)

:fill(fff,0)/p7i.vogel.de/companies/68/b9/68b9bb61e8f14/ic-logo-black-green.png)

:quality(80)/p7i.vogel.de/wcms/17/65/1765d3c52a763eb05766ac1ffb78faad/0127400733v1.jpeg)

:quality(80)/p7i.vogel.de/wcms/fe/18/fe181da82b3e76596f4d461a5920a33a/0129473576v1.jpeg)